Route two matched capacitors, C1 and C2, drawn in a capacitor matrix. More...

Public Member Functions | |

| def | __setStretching__ (self) |

| Sets vertical stretching value considering spacing between elementary capacitors in the matrix. More... | |

| def | setRules (self) |

| Defines technology rules used to draw the layout. More... | |

| def | drawVRoutingTracks (self, vRoutingTracksLayer) |

Iteratively draws vertical routing tracks given the physical layer vRoutingTracksLayer. More... | |

Public Member Functions inherited from CapacitorStack Public Member Functions inherited from CapacitorStack | |

| def | __init__ (self, device, capacitance, capacitorType, abutmentBoxPosition, nets, unitCap=0, matrixDim=[1, 1], matchingMode=False, matchingScheme=[], dummyRing=False, dummyElement=False) |

| This is the class constructor. More... | |

| def | __isUnitCap__ (self) |

| def | __isMatchingSchemeOK__ (self) |

| def | capacitorIdOccurence (self, capacitorIdentifier) |

| def | create (self, bbMode=False) |

| Draw the compact or matrix of capacitors. More... | |

| def | capacitorLine (self, dy, abutmentBox_spacing, matchingSchemeRowIndex=0) |

Iteratively draws a horizontal or vertical line of capacitors according to the direction parameter. More... | |

| def | capacitorMatrix (self, abutmentBox_spacing=0) |

| Draws a matrix of identical capacitors. More... | |

| def | drawAbutmentBox (self, abutmentBox_spacing=0) |

| Draws the abutment box of the matrix or campact capacitor. More... | |

| def | drawBottomPlatesRLayers (self, bottomPlateRLayer, drawnCapacitor) |

| Draws the routing layers connecting the bottom plate in the matrix of capacitors. More... | |

| def | drawTopPlatesRLayers (self, topPlateRLayer, drawnCapacitor) |

| Draws the routing layers connecting the top plates in the matrix of capacitors. More... | |

| def | getVerticalRoutingTrack_width (self) |

| def | getMatrixDim (self) |

| def | getMatchingScheme (self) |

Public Member Functions inherited from CapacitorUnit Public Member Functions inherited from CapacitorUnit | |

| def | __init__ (self, device, capacitorType, abutmentBoxPosition, capacitance=0, capDim={}) |

| This is the class constructor. More... | |

| def | __setCapacitorPerUnit__ (self, capacitorType) |

Sets the area and perimeter capacitances as specified in 350 nm AMS technology and according to capacitorType (MIM or PIP). More... | |

| def | __computeCapDim__ (self, capacitance, capacitorType) |

| Computes width and length of the capacitor. More... | |

| def | __isCapacitorUnitOK__ (self, capDim) |

| Checks if the computed capacitor dimensions exceed or are less than maximum and minimum limits, respectively, as specified in technology rules. More... | |

| def | getCapacitorType (self) |

| def | getMaximumCapWidth (self) |

| def | getMinimumCapWidth (self) |

| def | getLayers (self) |

| Loads the technology file then extracts the adequate layers according to the capacitor type (MIM or PIP). More... | |

| def | create (self, t, b, bbMode=False, vEnclosure_botPlate_abtBox=None, hEnclosure_botPlate_abtBox=None) |

| When bonding box mode is activated, the function draws all layout physical layers of the capacitor after checking its dimensions. More... | |

| def | drawCapacitor (self, layerDict, t, b) |

| Draws all layout physicial layers of the capacitor. More... | |

| def | computeBottomPlateCuts (self) |

| Computes needed parameters to draw bottom plate cuts in its exact position, including : More... | |

| def | computeTopPlateCuts (self) |

| Computes needed parameters to draw top plate cuts in its exact position, including : More... | |

| def | drawAbutmentBox (self) |

Draws the abutment box of the capacitor in position <(abutmentBoxXMin, abutmentBoxYMin)>. More... | |

| def | drawOnePlate (self, layer, net, boxDimensions) |

| Draws the top or bottom plate through inflation of the Box under it. More... | |

| def | drawBottomPlateCut (self, layer, b) |

| Draws the required cuts to connect the bottom plate. More... | |

| def | drawTopPlateCut (self, layer, t) |

| Draws the top plate's cuts after computing the maximal number of cuts that can be placed and its exact enclosure in the top plate. More... | |

| def | drawRoutingLayers (self, bottomPlateLayer, topPlateLayer, t, b) |

| Draws the routing layers of both bottom and top plates after computing widths and the exact position of these layers. More... | |

| def | cutMaxNumber (self, width_layer, width_cut, spacing_cut, enclosure_cut) |

Computes the maximal number of cuts to be placed on a layer of width width_layer considering specifications such as the spacing between the cuts, its width and its enclosure in the layer. More... | |

| def | cutLine (self, net, layer, firstCutXCenter, firstCutYCenter, width_cut, height_cut, spacing_cut, cutNumber, direction) |

| Creates a horizontal or vertical line of contacts according to the specified direction. More... | |

| def | cutMatrix (self, net, layer, firstCutXCenter, firstCutYCenter, width_cut, height_cut, spacing_cut, cutColumnNumber, cutRowNumber) |

| Creates a matrix of cuts by vertically stacking horizontal lines of identical cuts. More... | |

| def | getBottomPlateYMax (self) |

| def | getBottomPlateLeftCutXMin (self) |

| def | getBottomPlateLeftCutYMin (self) |

| def | getBottomPlateLeftCutYMax (self) |

| def | getBottomPlateRightCutXMin (self) |

| def | getBottomPlateRightCutYMin (self) |

| def | getBottomPlateRightCutYMax (self) |

| def | getBotPlateLeftRLayerXMax (self) |

| def | getBottomPlateRightCutYCenter (self) |

| def | getBotPlateLeftRLayerXMin (self) |

| def | getBotPlateRLayerYMin (self) |

| def | getBotPlateRLayerYMax (self) |

| def | getBotPlateRLayerWidth (self) |

| def | getBotPlateRightRLayerXCenter (self) |

| def | getBotPlateLeftRLayerXCenter (self) |

| def | getTopPlateRLayerYMin (self) |

| def | getTopPlateRLayerYMax (self) |

| def | getTopPlateRLayerWidth (self) |

| def | getTopPlateRLayerXCenter (self) |

| def | getTopPlateRLayerXMin (self) |

| def | getTopPlateRLayerXMax (self) |

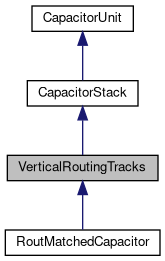

Detailed Description

Route two matched capacitors, C1 and C2, drawn in a capacitor matrix.

Connections are put in place with reference to a given matching scheme. Elementary capacitor units are connected to horizontal and vertical routing tracks that represent top plates and bottom plates nets of C1 and C2. Supported types of capacitors are Poly-Poly and Metal-Metal. Technologycal rules are provided by 350 nm AMS CMOS technology with three-four metal layers. Metal layers that are used for routeing are placed similarly to horziontal-vertical (HV) symbolic Alliance CAD tool router, where horizontal metal channels are drawn in metal 2 and the vertical ones are in metal 3. Given a matrix of dimensions ![]() , the total number of vertical tracks is

, the total number of vertical tracks is ![]() equivalent to

equivalent to ![]() couples, ensuring that every elementary capacitor is positioned between four vertical tracks, two from each side. In fact, every adjacent couple of these tracks represent top plates and bottom plates of C1 or C2 as shown in Figure 1.

couples, ensuring that every elementary capacitor is positioned between four vertical tracks, two from each side. In fact, every adjacent couple of these tracks represent top plates and bottom plates of C1 or C2 as shown in Figure 1.

An elementary capacitor unit can be a part of C1 or C2 according to the matching scheme. However, to respect common-centroid layout specifications, for C1 and C2 to be equal, the matrix number of colums and number of rows must be both even. Addionnally, the number of elementary capacitors dedicated to C1 must be equal to those dedicated to C2. These two conditions are tested in one of the class methods. An exception is raised if at least one of the two is not respected.

Member Function Documentation

◆ __setStretching__()

| def __setStretching__ | ( | self | ) |

Sets vertical stretching value considering spacing between elementary capacitors in the matrix.

- Returns

- stratching value.

References CapacitorStack.abutmentBox_spacing, RoutMatchedCapacitor.abutmentBox_spacing, and VerticalRoutingTracks.abutmentBox_spacing.

Referenced by RoutMatchedCapacitor.computeHRLayerYCenter(), and VerticalRoutingTracks.drawVRoutingTracks().

◆ setRules()

| def setRules | ( | self | ) |

Defines technology rules used to draw the layout.

Some of the rules, namely those describing routeing layers and tracks are applicable for both MIM and PIP capacitors. However, cuts rules are different.

- Remark:

- All

CapacitorStackclass rules are also reloaded in this class. An exception is raised if the entered capacitor type is unsupported.

- Returns

- a dictionary with rules labels as keys and rules content as values.

Reimplemented from CapacitorStack.

Reimplemented in RoutMatchedCapacitor.

References VerticalRoutingTracks.capacitorInstance, CapacitorStack.capacitorsNumber, VerticalRoutingTracks.capacitorsNumber, VerticalRoutingTracks.computeVRTDimensions(), VerticalRoutingTracks.drawVRoutingTracks(), VerticalRoutingTracks.minEnclosure_hRoutingLayer_vRoutingTrack_cut, VerticalRoutingTracks.minEnclosure_hRoutingTrackCut, VerticalRoutingTracks.minimizeVRTs(), RoutMatchedCapacitor.minSpacing_hRoutingTrack, VerticalRoutingTracks.minSpacing_hRoutingTrack, VerticalRoutingTracks.minWidth_hRoutingLayer, VerticalRoutingTracks.minWidth_hRoutingLayer_vRoutingTrack_cut, VerticalRoutingTracks.minWidth_hRoutingTrack, VerticalRoutingTracks.minWidth_hRoutingTrackCut, CapacitorStack.setRules(), RoutMatchedCapacitor.setRules(), CapacitorUnit.setRules(), and VerticalRoutingTracks.setRules().

Referenced by CapacitorStack.create(), CapacitorUnit.create(), RoutMatchedCapacitor.route(), and VerticalRoutingTracks.setRules().

◆ drawVRoutingTracks()

| def drawVRoutingTracks | ( | self, | |

| vRoutingTracksLayer | |||

| ) |

Iteratively draws vertical routing tracks given the physical layer vRoutingTracksLayer.

Every elementary capacitor is consequently positioned between four routing tracks, two from each side. Each couple of adjacent routeing tracks represent top plate and bottom plate nets of Ci, where i is in [1,2]. As given in Figure 2, capacitor ![]() with an even j value situated in even columns have and inversely for odd columns numbers.

with an even j value situated in even columns have and inversely for odd columns numbers.

References VerticalRoutingTracks.__computeVRTsNumber__(), VerticalRoutingTracks.__findCapIdsToEliminate__(), VerticalRoutingTracks.__findCapIdsToEliminatePerColumn__(), VerticalRoutingTracks.__findUsedCapIdsPerColumn__(), VerticalRoutingTracks.__findVRTsToEliminate__(), VerticalRoutingTracks.__setNetsDistribution__(), VerticalRoutingTracks.__setPlatesDistribution__(), VerticalRoutingTracks.__setStretching__(), VerticalRoutingTracks.__setVRTsDistribution__(), CapacitorStack.abutmentBox, CapacitorUnit.abutmentBox, VerticalRoutingTracks.abutmentBox, CapacitorStack.abutmentBox_spacing, RoutMatchedCapacitor.abutmentBox_spacing, VerticalRoutingTracks.abutmentBox_spacing, VerticalRoutingTracks.capacitorIds, VerticalRoutingTracks.capacitorInstance, CapacitorStack.capacitorsNumber, VerticalRoutingTracks.capacitorsNumber, VerticalRoutingTracks.computeXCenters(), CapacitorStack.dummyElement, RoutMatchedCapacitor.dummyElement, VerticalRoutingTracks.dummyElement, CapacitorStack.dummyRing, RoutMatchedCapacitor.dummyRing, VerticalRoutingTracks.dummyRing, VerticalRoutingTracks.getVTrackYMax(), VerticalRoutingTracks.getVTrackYMin(), CapacitorUnit.hpitch, RoutMatchedCapacitor.hRoutingTrack_width, VerticalRoutingTracks.hRoutingTrack_width, CapacitorStack.matchingScheme, VerticalRoutingTracks.matchingScheme, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, RoutMatchedCapacitor.maximumPosition, VerticalRoutingTracks.maximumPosition, CapacitorUnit.metal2Width, VerticalRoutingTracks.minEnclosure_hRoutingTrackCut, VerticalRoutingTracks.minimizeVRT, RoutMatchedCapacitor.minimumPosition, VerticalRoutingTracks.minimumPosition, VerticalRoutingTracks.minWidth_hRoutingTrack, VerticalRoutingTracks.minWidth_hRoutingTrackCut, CapacitorStack.nets, VerticalRoutingTracks.nets, VerticalRoutingTracks.platesDistribution, CapacitorStack.vRoutingTrack_width, VerticalRoutingTracks.vRoutingTrack_width, RoutMatchedCapacitor.vRoutingTrackDict, VerticalRoutingTracks.vRoutingTrackDict, RoutMatchedCapacitor.vRoutingTrackXCenter, VerticalRoutingTracks.vRoutingTrackXCenter, RoutMatchedCapacitor.vRTsDistribution, VerticalRoutingTracks.vRTsDistribution, and VerticalRoutingTracks.vRTsToEliminate.

Referenced by VerticalRoutingTracks.setRules().

The documentation for this class was generated from the following file:

- capacitorvrtracks.py