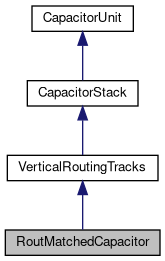

Routs two matched capacitors, C1 and C2, drawn in a capacitor matrix. More...

Public Member Functions | |

| def | __init__ (self, vRTInstance) |

| A special method used to customize the class instance to an initial state in which : More... | |

| def | route (self, bbMode=False) |

| Draws the complete layout given the capacitor matrix. More... | |

| def | setRules (self) |

| Defines technology rules used to draw the layout. More... | |

| def | setLayers (self) |

| Defines all physical layers used to draw the layout. More... | |

| def | computeDimensions (self, bbMode) |

| Computes, through simple instructions and functions calls, layout variables detailed in Figure 2. More... | |

| def | computeHRoutingTrackYCenter (self) |

| Computes centers' ordinates of the eight horizontal routing tracks. More... | |

| def | computeHRLayerYCenter (self) |

| Sets the stretching value of top plates. More... | |

| def | drawHRoutingTracks (self, routingTracksLayer) |

Iteratively draws horizontal routing tracks on top and bottom positions of the matrix using physical layer routingTracksLayer. More... | |

| def | drawHRLayers (self, xPlateRLayer) |

| Iteratively draws the horizontal routing layers starting with bottom left elementary capacitor | |

| def | drawCuts (self, layer_hRTrack_hRLayer, layer_tracksCut, layer_topPlateCut) |

| Draws all required cuts using physical layers : More... | |

| def | drawOneCut_vRoutingTrack_HRLayer (self, net, cutLayer, cutXMin, cutYMin, cutNumber) |

Draws one cut, in layer cutLayer, in order to connect a vertical routing track, at position cutXMin in metal 2, and a horizontal routing track, at position cutYMin in metal 3. More... | |

| def | drawCuts_vRoutingTrack_hRoutingTrack (self, cutLayer, cutNumber, enclosure_cut) |

| Draws cuts to connect vertical routing tracks in metal 2 and horizontal routing tracks in metal 3. More... | |

| def | __stretchTopPlates__ (self, capacitor, rlayer) |

| Iteratively performs top plates stretching for the capacitor matrix. More... | |

| def | __stretchTopPlateCompactCap__ (self, net, capacitor, routingLayer, j=0) |

| Draws vertical stretched layers for a given elementary capacitor. More... | |

| def | __setStretchingDySourceDyTarget__ (self, capacitor, deltay) |

| Sets the abcissas of the extremities of the vertical stretching to be applied to capacitor's top plates for a given elementary capacitor in the matrix. More... | |

| def | __computeConnections__ (self, i, j, capacitorIdentifier) |

| Computes horizontal routing layers source and target abcissas for top and bottom plates connections to its associated routing track. More... | |

Public Member Functions inherited from VerticalRoutingTracks Public Member Functions inherited from VerticalRoutingTracks | |

| def | __setStretching__ (self) |

| Sets vertical stretching value considering spacing between elementary capacitors in the matrix. More... | |

| def | drawVRoutingTracks (self, vRoutingTracksLayer) |

Iteratively draws vertical routing tracks given the physical layer vRoutingTracksLayer. More... | |

Public Member Functions inherited from CapacitorStack Public Member Functions inherited from CapacitorStack | |

| def | __init__ (self, device, capacitance, capacitorType, abutmentBoxPosition, nets, unitCap=0, matrixDim=[1, 1], matchingMode=False, matchingScheme=[], dummyRing=False, dummyElement=False) |

| This is the class constructor. More... | |

| def | __isUnitCap__ (self) |

| def | __isMatchingSchemeOK__ (self) |

| def | capacitorIdOccurence (self, capacitorIdentifier) |

| def | create (self, bbMode=False) |

| Draw the compact or matrix of capacitors. More... | |

| def | capacitorLine (self, dy, abutmentBox_spacing, matchingSchemeRowIndex=0) |

Iteratively draws a horizontal or vertical line of capacitors according to the direction parameter. More... | |

| def | capacitorMatrix (self, abutmentBox_spacing=0) |

| Draws a matrix of identical capacitors. More... | |

| def | drawAbutmentBox (self, abutmentBox_spacing=0) |

| Draws the abutment box of the matrix or campact capacitor. More... | |

| def | drawBottomPlatesRLayers (self, bottomPlateRLayer, drawnCapacitor) |

| Draws the routing layers connecting the bottom plate in the matrix of capacitors. More... | |

| def | drawTopPlatesRLayers (self, topPlateRLayer, drawnCapacitor) |

| Draws the routing layers connecting the top plates in the matrix of capacitors. More... | |

| def | getVerticalRoutingTrack_width (self) |

| def | getMatrixDim (self) |

| def | getMatchingScheme (self) |

Public Member Functions inherited from CapacitorUnit Public Member Functions inherited from CapacitorUnit | |

| def | __init__ (self, device, capacitorType, abutmentBoxPosition, capacitance=0, capDim={}) |

| This is the class constructor. More... | |

| def | __setCapacitorPerUnit__ (self, capacitorType) |

Sets the area and perimeter capacitances as specified in 350 nm AMS technology and according to capacitorType (MIM or PIP). More... | |

| def | __computeCapDim__ (self, capacitance, capacitorType) |

| Computes width and length of the capacitor. More... | |

| def | __isCapacitorUnitOK__ (self, capDim) |

| Checks if the computed capacitor dimensions exceed or are less than maximum and minimum limits, respectively, as specified in technology rules. More... | |

| def | getCapacitorType (self) |

| def | getMaximumCapWidth (self) |

| def | getMinimumCapWidth (self) |

| def | getLayers (self) |

| Loads the technology file then extracts the adequate layers according to the capacitor type (MIM or PIP). More... | |

| def | create (self, t, b, bbMode=False, vEnclosure_botPlate_abtBox=None, hEnclosure_botPlate_abtBox=None) |

| When bonding box mode is activated, the function draws all layout physical layers of the capacitor after checking its dimensions. More... | |

| def | drawCapacitor (self, layerDict, t, b) |

| Draws all layout physicial layers of the capacitor. More... | |

| def | computeBottomPlateCuts (self) |

| Computes needed parameters to draw bottom plate cuts in its exact position, including : More... | |

| def | computeTopPlateCuts (self) |

| Computes needed parameters to draw top plate cuts in its exact position, including : More... | |

| def | drawAbutmentBox (self) |

Draws the abutment box of the capacitor in position <(abutmentBoxXMin, abutmentBoxYMin)>. More... | |

| def | drawOnePlate (self, layer, net, boxDimensions) |

| Draws the top or bottom plate through inflation of the Box under it. More... | |

| def | drawBottomPlateCut (self, layer, b) |

| Draws the required cuts to connect the bottom plate. More... | |

| def | drawTopPlateCut (self, layer, t) |

| Draws the top plate's cuts after computing the maximal number of cuts that can be placed and its exact enclosure in the top plate. More... | |

| def | drawRoutingLayers (self, bottomPlateLayer, topPlateLayer, t, b) |

| Draws the routing layers of both bottom and top plates after computing widths and the exact position of these layers. More... | |

| def | cutMaxNumber (self, width_layer, width_cut, spacing_cut, enclosure_cut) |

Computes the maximal number of cuts to be placed on a layer of width width_layer considering specifications such as the spacing between the cuts, its width and its enclosure in the layer. More... | |

| def | cutLine (self, net, layer, firstCutXCenter, firstCutYCenter, width_cut, height_cut, spacing_cut, cutNumber, direction) |

| Creates a horizontal or vertical line of contacts according to the specified direction. More... | |

| def | cutMatrix (self, net, layer, firstCutXCenter, firstCutYCenter, width_cut, height_cut, spacing_cut, cutColumnNumber, cutRowNumber) |

| Creates a matrix of cuts by vertically stacking horizontal lines of identical cuts. More... | |

| def | getBottomPlateYMax (self) |

| def | getBottomPlateLeftCutXMin (self) |

| def | getBottomPlateLeftCutYMin (self) |

| def | getBottomPlateLeftCutYMax (self) |

| def | getBottomPlateRightCutXMin (self) |

| def | getBottomPlateRightCutYMin (self) |

| def | getBottomPlateRightCutYMax (self) |

| def | getBotPlateLeftRLayerXMax (self) |

| def | getBottomPlateRightCutYCenter (self) |

| def | getBotPlateLeftRLayerXMin (self) |

| def | getBotPlateRLayerYMin (self) |

| def | getBotPlateRLayerYMax (self) |

| def | getBotPlateRLayerWidth (self) |

| def | getBotPlateRightRLayerXCenter (self) |

| def | getBotPlateLeftRLayerXCenter (self) |

| def | getTopPlateRLayerYMin (self) |

| def | getTopPlateRLayerYMax (self) |

| def | getTopPlateRLayerWidth (self) |

| def | getTopPlateRLayerXCenter (self) |

| def | getTopPlateRLayerXMin (self) |

| def | getTopPlateRLayerXMax (self) |

Detailed Description

Routs two matched capacitors, C1 and C2, drawn in a capacitor matrix.

Connections are put in place with reference to a given matching scheme. Elementary capacitor units are connected to horizontal and vertical routing tracks that represent top plates and bottom plates nets of C1 and C2 . Supported types of capacitors are Poly-Poly and Metal-Metal. Technologycal rules are provided by 350 nm AMS CMOS technology with three-four metal layers. Metal layers that are used for routing are placed similarly to horziontal-vertical (HV) symbolic Alliance CAD tool router, where horizontal metal channels are drawn in metal 2 and the vertical ones are in metal 3. Given a matrix of dimensions ![]() , the total number of vertical tracks is

, the total number of vertical tracks is ![]() equivalent to

equivalent to ![]() couples, ensuring that every elementary capacitor is positioned between four vertical tracks, two from each side. In fact, every adjacent couple of these tracks represent top plates and bottom plates of C1 or C2 as shown in Figure 1.

couples, ensuring that every elementary capacitor is positioned between four vertical tracks, two from each side. In fact, every adjacent couple of these tracks represent top plates and bottom plates of C1 or C2 as shown in Figure 1.

An elementary capacitor unit can be a part of C1 or C2 according to the matching scheme. However, to respect common-centroid layout specifications, for C1 and C2 to be equal, the matrix number of colums and number of rows must be both even. Addionnally, the number of elementary capacitors dedicated to C1 must be equal to those dedicated to C2. These two conditions are tested in one of the class methods. An exception is raised if at least one of the two is not respected.

Constructor & Destructor Documentation

◆ __init__()

| def __init__ | ( | self, | |

| vRTInstance | |||

| ) |

A special method used to customize the class instance to an initial state in which :

- the class attirbutes describing positions and dimensions of the layout are computed in dedicated class methods,

- the attributes related to the capacitor matrix are copied from the

CapacitorStackinstance.

Position and dimensions attributes, also refered by layout variables, in Figure 2, are defined below :

- Parameters

-

device The Hurricane AMS device onto which the layout is drawn. capacitorInstance Instance of CapacitorStackclass.capacitor A nested list containing the matrix elements, which are CapacitorUnitobjects.matchingScheme A nested list, with equal dimensions as capacitorattribute, containing assignements of matrix elementary units to C1 and C2, identified by 1 and 2, respectively. Therefore,self.matchingSchemecontent is a succession of 1 and 2 values, defined as \ capacitor identifiers. For example, given a matrix of dimensions 2x2, the matching scheme can be![$ [ [1,2], [1,2] ] or [ [2,1], [2,1] ] $](form_14.png) . The first sub-list dictates that the first elementary capacitor,

. The first sub-list dictates that the first elementary capacitor,  . The second element

. The second element  is affected to C2 and so on. An immediate and obvious consequence to this, is that an error is raised if

is affected to C2 and so on. An immediate and obvious consequence to this, is that an error is raised if self.matchingSchemandself.capacitordimensions are not identical or ifself.matchingSchemecontent is different from supported capacitor identifiers, '1' and '2'.capacitorType Supported types of capacitors are MIM and PIP only. An exception is raised otherwise. abutmentBox The matrix's abutment box. matrxiDim The matrix dimensions, also equal to self.matchingSchemenested list dimensions.abutmentBox_spacing The spacing between elementary units in the matrix. It is computed in CapacitorStackand is reloaded inRoutMatchedCapacitor.self.abutmentBox_spacingincludes, vertical routing tracks width and minimum allowed spacing between two adjacent ones.hRoutingLayer_width The width of horizontal routing layers in metal 2, which connect capacitors plates to vertical routing tracks. vRoutingTrack_width The width of vertical routing tracks in metal 3, which connects identical nets together ( ie : bottom plates of C1, top plates of C2, bottom plates of C2 and top plates of C2 ). hRoutingTrack_width The width of horizontal routing tracks in metal 2, which connect identical vertical routing tracks together. minSpacing_hRoutingTrack Minimum spacing between horizontal routing tracks. Wide metal 2 specifications are considered since metal 2 dimensions may exceed 10  .

.

- Remark:

- For more information about wide metal specifications, refer to ENG-183_rev8.pdf technology manual.

- Parameters

-

minimumPosition The ordinate of the top plate's routing layer's bottom extremity after stretching. maximumPosition The ordinate of the top plate's routing layer's top extremity, also equivalent to the top plate's top extremity. vRoutingTrackXCenter A nested list of ordered dictionaries, with dimensions equal to self.matrixDim, containing abcissas of vertical routing tracks. All sub-lists' lengths are identical and are equal to 2. The first and second elements describe position of top plate track and bottom plate track, respectively. For example, given a matrix of dimensions 2x2,self.vRoutingTrackXCentercan be [[0, 2], [4,6], [8,10]] . Elements of this nested list have particular indexing as described in Figure 2.

. Elements of this nested list have particular indexing as described in Figure 2.hRoutingtrackYCenter A nested dictonary containing two keys, topTracksandbottomTracks. Each key contains as value a dictionary describing centers' ordinates of four parallel horizontal tracks. The reason why four tracks are needed on top and bottom positions of the matrix is that four nets are used, two for every capacitorCi, wereiis in [1,2].hRoutingLayerYCenter A nested dicitonary containing two keys, topandbottom. Each key contains as value a dictionary describing centers' ordinates of horizontal routing layers.vRoutingTrackDict A dictionary of routing tracks top and bottom extremities ordinates. topPlateStretching Since not only the same metal 2 layer is used to draw top/bottom plates connections to vertical tracks but also the two plates are superimposed, the top plate's routing tracks is stretched. self.topPlateStretchingis therefore the length added to top plate's routing layer in order to avoid short circuits between top and bottom plates routing to vertical tracks since the same metal is used for both.

References RoutMatchedCapacitor.capacitor, VerticalRoutingTracks.capacitor, CapacitorStack.dummyRing, RoutMatchedCapacitor.dummyRing, VerticalRoutingTracks.dummyRing, RoutMatchedCapacitor.dummyRingCapacitor, RoutMatchedCapacitor.hRoutingLayer_width, RoutMatchedCapacitor.hRoutingLayerYCenter, RoutMatchedCapacitor.hRoutingTrack_width, VerticalRoutingTracks.hRoutingTrack_width, RoutMatchedCapacitor.hRoutingtrackYCenter, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, RoutMatchedCapacitor.maximumPosition, VerticalRoutingTracks.maximumPosition, RoutMatchedCapacitor.minimumPosition, VerticalRoutingTracks.minimumPosition, RoutMatchedCapacitor.minSpacing_hRoutingTrack, VerticalRoutingTracks.minSpacing_hRoutingTrack, RoutMatchedCapacitor.topPlateStretching, and RoutMatchedCapacitor.vRTInstance.

Member Function Documentation

◆ route()

| def route | ( | self, | |

bbMode = False |

|||

| ) |

Draws the complete layout given the capacitor matrix.

route method is succession of calls to user-defined methods inside a newly created Updatesession. The following tasks are excecuted :

- A nex

UpdateSessionis created, - all required physical layers are loaded,

- technology rules are defined according to capacitor type,

- layout dimension parameters are computed,

- routing tracks and layers are drawn,

- top plates are stretched,

- all required cuts are drawn,

- The

UpdateSessionis closed.

Meanwhile, an exception is raised when the entered capacitor is not a capacitor matrix or if the capacitor type is unsupported.

References CapacitorStack.__isUnitCap__(), RoutMatchedCapacitor.__stretchTopPlates__(), CapacitorStack.abutmentBox, CapacitorUnit.abutmentBox, VerticalRoutingTracks.abutmentBox, RoutMatchedCapacitor.capacitor, VerticalRoutingTracks.capacitor, VerticalRoutingTracks.capacitorInstance, Stack.computeDimensions(), RoutMatchedCapacitor.computeDimensions(), CapacitorUnit.computeDimensions(), CapacitorStack.device, CapacitorUnit.device, VerticalRoutingTracks.device, Stack.device, RoutMatchedCapacitor.drawCuts(), RoutMatchedCapacitor.drawDummyRing_hRTracks_Cuts(), RoutMatchedCapacitor.drawHRLayers(), RoutMatchedCapacitor.drawHRoutingTracks(), CapacitorStack.dummyRing, RoutMatchedCapacitor.dummyRing, VerticalRoutingTracks.dummyRing, RoutMatchedCapacitor.dummyRingCapacitor, CapacitorUnit.getBotPlateLeftRLayerXCenter(), CapacitorUnit.getBotPlateRightRLayerXCenter(), CapacitorUnit.getBotPlateRLayerWidth(), CapacitorUnit.getBotPlateRLayerYMin(), CapacitorUnit.getTopPlateRLayerWidth(), CapacitorUnit.getTopPlateRLayerYMin(), VerticalRoutingTracks.getVTrackYMax(), VerticalRoutingTracks.getVTrackYMin(), CapacitorUnit.hpitch, RoutMatchedCapacitor.hRoutingtrackYCenter, CapacitorStack.matchingScheme, VerticalRoutingTracks.matchingScheme, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, RoutMatchedCapacitor.maximumPosition, VerticalRoutingTracks.maximumPosition, CapacitorUnit.metal3Width, RoutMatchedCapacitor.minimumPosition, VerticalRoutingTracks.minimumPosition, CapacitorStack.nets, VerticalRoutingTracks.nets, RoutMatchedCapacitor.routeDummyRing(), RoutMatchedCapacitor.routeLeftAndRightSides(), RoutMatchedCapacitor.routeTopOrBottomSide(), RoutMatchedCapacitor.setLayers(), CapacitorStack.setRules(), RoutMatchedCapacitor.setRules(), CapacitorUnit.setRules(), VerticalRoutingTracks.setRules(), CapacitorUnit.vpitch, CapacitorStack.vRoutingTrack_width, VerticalRoutingTracks.vRoutingTrack_width, RoutMatchedCapacitor.vRoutingTrackXCenter, and VerticalRoutingTracks.vRoutingTrackXCenter.

◆ setRules()

| def setRules | ( | self | ) |

Defines technology rules used to draw the layout.

Some of the rules, namely those describing routing layers and tracks are applicable for both MIM and PIP capacitors. However, cuts rules are different.

- Remark:

- All

CapacitorStackclass rules are also reloaded in this class. An exception is raised if the entered capacitor type is unsupported.

- Returns

- a dictionary with rules labels as keys and rules content as values.

Reimplemented from VerticalRoutingTracks.

References CapacitorStack.capacitorType, RoutMatchedCapacitor.capacitorType, CapacitorUnit.capacitorType, VerticalRoutingTracks.capacitorType, CapacitorStack.minEnclosure_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minEnclosure_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minSpacing_hRoutingLayer, RoutMatchedCapacitor.minSpacing_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minSpacing_hRoutingLayer_vRoutingTrack_cut, RoutMatchedCapacitor.minSpacing_hRoutingTrackCut, CapacitorStack.minSpacing_vRoutingTrackCut, RoutMatchedCapacitor.minSpacing_vRoutingTrackCut, CapacitorStack.minWidth_hRoutingLayer_topPlate_cut, and RoutMatchedCapacitor.minWidth_hRoutingLayer_topPlate_cut.

Referenced by CapacitorStack.create(), CapacitorUnit.create(), RoutMatchedCapacitor.route(), and VerticalRoutingTracks.setRules().

◆ setLayers()

| def setLayers | ( | self | ) |

Defines all physical layers used to draw the layout.

Layers are loaded using DataBase API. The same routing layers are used for both capacitor types except cuts layers that connect top plates to vertical routing tracks. Basicaly, metal 2, meta 3, cut 1 and cut 2 are the ones defined.

- Returns

- a dictionary composed of layers labels as keys and layers as values.

References CapacitorStack.capacitorType, RoutMatchedCapacitor.capacitorType, CapacitorUnit.capacitorType, VerticalRoutingTracks.capacitorType, CapacitorStack.dummyRing, RoutMatchedCapacitor.dummyRing, and VerticalRoutingTracks.dummyRing.

Referenced by RoutMatchedCapacitor.route().

◆ computeDimensions()

| def computeDimensions | ( | self, | |

| bbMode | |||

| ) |

Computes, through simple instructions and functions calls, layout variables detailed in Figure 2.

References CapacitorStack.abutmentBox_spacing, RoutMatchedCapacitor.abutmentBox_spacing, VerticalRoutingTracks.abutmentBox_spacing, VerticalRoutingTracks.capacitorInstance, CapacitorStack.capacitorsNumber, VerticalRoutingTracks.capacitorsNumber, RoutMatchedCapacitor.computeBondingBoxDimInbbMode(), RoutMatchedCapacitor.computeHRLayerYCenter(), RoutMatchedCapacitor.computeHRoutingTrackYCenter(), RoutMatchedCapacitor.hRoutingLayer_width, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, RoutMatchedCapacitor.maximumPosition, VerticalRoutingTracks.maximumPosition, CapacitorStack.minEnclosure_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minEnclosure_hRoutingLayer_topPlate_cut, VerticalRoutingTracks.minEnclosure_hRoutingLayer_vRoutingTrack_cut, RoutMatchedCapacitor.minimumPosition, VerticalRoutingTracks.minimumPosition, VerticalRoutingTracks.minWidth_hRoutingLayer, CapacitorStack.minWidth_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minWidth_hRoutingLayer_topPlate_cut, VerticalRoutingTracks.minWidth_hRoutingLayer_vRoutingTrack_cut, RoutMatchedCapacitor.vRoutingTrack_spacing, CapacitorStack.vRoutingTrack_width, VerticalRoutingTracks.vRoutingTrack_width, RoutMatchedCapacitor.vRoutingTrackDict, VerticalRoutingTracks.vRoutingTrackDict, RoutMatchedCapacitor.vRoutingTrackXCenter, VerticalRoutingTracks.vRoutingTrackXCenter, and RoutMatchedCapacitor.vRTInstance.

Referenced by CapacitorUnit.create(), Stack.doLayout(), RoutMatchedCapacitor.route(), and Stack.setWirings().

◆ computeHRoutingTrackYCenter()

| def computeHRoutingTrackYCenter | ( | self | ) |

Computes centers' ordinates of the eight horizontal routing tracks.

The tracks include four on top and four on bottom of the matrix. To do the computations, fist, center of the first bottom or top track, given in Figure 2, is computed. Then, all adjacent three centers are deduced by simples translation of the first one. Translation quantity is equal to the sum of distance between adjacent routing tracks, self.hRoutingTracks_spacing, and half width of the routing track itself, self.hRoutingTrack_width.

References RoutMatchedCapacitor.__setPlatesIds__(), CapacitorUnit.hpitch, RoutMatchedCapacitor.hRoutingtrackYCenter, RoutMatchedCapacitor.maximumPosition, VerticalRoutingTracks.maximumPosition, RoutMatchedCapacitor.minimumPosition, and VerticalRoutingTracks.minimumPosition.

Referenced by RoutMatchedCapacitor.computeDimensions().

◆ computeHRLayerYCenter()

| def computeHRLayerYCenter | ( | self | ) |

Sets the stretching value of top plates.

Then iteratively computes the centers of horizontal routing layer regarding top and bottom plates.

References RoutMatchedCapacitor.__findPossibleShortCircuits__(), VerticalRoutingTracks.__setStretching__(), RoutMatchedCapacitor.__setStretchingDySourceDyTarget__(), RoutMatchedCapacitor.bondingBox, RoutMatchedCapacitor.capacitor, VerticalRoutingTracks.capacitor, CapacitorUnit.getBottomPlateRightCutYMax(), CapacitorUnit.getBottomPlateRightCutYMin(), RoutMatchedCapacitor.hRoutingLayer_width, RoutMatchedCapacitor.hRoutingLayerYCenter, RoutMatchedCapacitor.hRoutingTrack_width, VerticalRoutingTracks.hRoutingTrack_width, RoutMatchedCapacitor.hRoutingtrackYCenter, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, RoutMatchedCapacitor.minSpacing_hRoutingLayer, RoutMatchedCapacitor.topPlateStretching, CapacitorStack.vRoutingTrack_width, VerticalRoutingTracks.vRoutingTrack_width, RoutMatchedCapacitor.vRoutingTrackXCenter, and VerticalRoutingTracks.vRoutingTrackXCenter.

Referenced by RoutMatchedCapacitor.computeDimensions().

◆ drawHRoutingTracks()

| def drawHRoutingTracks | ( | self, | |

| routingTracksLayer | |||

| ) |

Iteratively draws horizontal routing tracks on top and bottom positions of the matrix using physical layer routingTracksLayer.

References CapacitorStack.device, CapacitorUnit.device, VerticalRoutingTracks.device, Stack.device, RoutMatchedCapacitor.hRoutingTrack_width, VerticalRoutingTracks.hRoutingTrack_width, RoutMatchedCapacitor.hRoutingtrackYCenter, CapacitorStack.nets, VerticalRoutingTracks.nets, RoutMatchedCapacitor.vRoutingTrackXCenter, and VerticalRoutingTracks.vRoutingTrackXCenter.

Referenced by RoutMatchedCapacitor.route().

◆ drawHRLayers()

| def drawHRLayers | ( | self, | |

| xPlateRLayer | |||

| ) |

Iteratively draws the horizontal routing layers starting with bottom left elementary capacitor ![]() .

.

References RoutMatchedCapacitor.__computeConnections__(), RoutMatchedCapacitor.hRoutingLayer_width, RoutMatchedCapacitor.hRoutingLayerYCenter, CapacitorStack.matchingScheme, VerticalRoutingTracks.matchingScheme, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, CapacitorStack.nets, and VerticalRoutingTracks.nets.

Referenced by RoutMatchedCapacitor.route().

◆ drawCuts()

| def drawCuts | ( | self, | |

| layer_hRTrack_hRLayer, | |||

| layer_tracksCut, | |||

| layer_topPlateCut | |||

| ) |

Draws all required cuts using physical layers :

layer_hRTrack_hRLayerto connect bottom plates to vertical routing tracks,layer_tracksCutto connect vertical routing tracks to horizontal ones,layer_topPlateCutto connect top plates to vertical routing tracks. ALso indrawCuts, nUmber of maximum cuts number on every layer is computed and cuts enclosure is adjusted according to layer's width.

References RoutMatchedCapacitor.__setPlatesLabels__(), VerticalRoutingTracks.capacitorIds, CapacitorStack.capacitorsNumber, VerticalRoutingTracks.capacitorsNumber, RoutMatchedCapacitor.drawCuts_stretchedTopPlate(), RoutMatchedCapacitor.drawCuts_vRoutingTrack_HRLayer(), RoutMatchedCapacitor.drawCuts_vRoutingTrack_hRoutingTrack(), RoutMatchedCapacitor.drawOneCut_vRoutingTrack_HRLayer(), RoutMatchedCapacitor.hRoutingLayerYCenter, CapacitorStack.matchingScheme, VerticalRoutingTracks.matchingScheme, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, CapacitorStack.minEnclosure_vRoutingTrackCut, RoutMatchedCapacitor.minSpacing_hRoutingTrackCut, CapacitorStack.minSpacing_vRoutingTrackCut, RoutMatchedCapacitor.minSpacing_vRoutingTrackCut, VerticalRoutingTracks.minWidth_hRoutingTrackCut, CapacitorStack.minWidth_vRoutingTrackCut, CapacitorStack.nets, VerticalRoutingTracks.nets, CapacitorStack.vRoutingTrack_width, VerticalRoutingTracks.vRoutingTrack_width, RoutMatchedCapacitor.vRoutingTrackXCenter, and VerticalRoutingTracks.vRoutingTrackXCenter.

Referenced by RoutMatchedCapacitor.route().

◆ drawOneCut_vRoutingTrack_HRLayer()

| def drawOneCut_vRoutingTrack_HRLayer | ( | self, | |

| net, | |||

| cutLayer, | |||

| cutXMin, | |||

| cutYMin, | |||

| cutNumber | |||

| ) |

Draws one cut, in layer cutLayer, in order to connect a vertical routing track, at position cutXMin in metal 2, and a horizontal routing track, at position cutYMin in metal 3.

References RoutMatchedCapacitor.minSpacing_hRoutingLayer_vRoutingTrack_cut, and VerticalRoutingTracks.minWidth_hRoutingLayer_vRoutingTrack_cut.

Referenced by RoutMatchedCapacitor.drawCuts().

◆ drawCuts_vRoutingTrack_hRoutingTrack()

| def drawCuts_vRoutingTrack_hRoutingTrack | ( | self, | |

| cutLayer, | |||

| cutNumber, | |||

| enclosure_cut | |||

| ) |

Draws cuts to connect vertical routing tracks in metal 2 and horizontal routing tracks in metal 3.

References RoutMatchedCapacitor.__setPlatesIds__(), RoutMatchedCapacitor.capacitor, VerticalRoutingTracks.capacitor, RoutMatchedCapacitor.dummyRingCapacitor, CapacitorUnit.getBotPlateRLayerWidth(), CapacitorUnit.getBottomPlateLeftCutXMin(), CapacitorUnit.getBottomPlateRightCutXMin(), CapacitorUnit.getTopPlateRLayerWidth(), CapacitorUnit.getTopPlateRLayerXMin(), RoutMatchedCapacitor.hRoutingLayerYCenter, RoutMatchedCapacitor.hRoutingtrackYCenter, CapacitorStack.matchingScheme, VerticalRoutingTracks.matchingScheme, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, CapacitorStack.minEnclosure_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minEnclosure_hRoutingLayer_topPlate_cut, CapacitorStack.minEnclosure_vRoutingTrackCut, RoutMatchedCapacitor.minSpacing_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minSpacing_hRoutingTrackCut, CapacitorStack.minSpacing_vRoutingTrackCut, RoutMatchedCapacitor.minSpacing_vRoutingTrackCut, CapacitorStack.minWidth_hRoutingLayer_topPlate_cut, RoutMatchedCapacitor.minWidth_hRoutingLayer_topPlate_cut, VerticalRoutingTracks.minWidth_hRoutingTrackCut, CapacitorStack.minWidth_vRoutingTrackCut, CapacitorStack.nets, VerticalRoutingTracks.nets, CapacitorStack.vRoutingTrack_width, VerticalRoutingTracks.vRoutingTrack_width, RoutMatchedCapacitor.vRoutingTrackXCenter, and VerticalRoutingTracks.vRoutingTrackXCenter.

Referenced by RoutMatchedCapacitor.drawCuts().

◆ __stretchTopPlates__()

| def __stretchTopPlates__ | ( | self, | |

| capacitor, | |||

| rlayer | |||

| ) |

Iteratively performs top plates stretching for the capacitor matrix.

Vertical segments are connected to top plate routing layer.

- Parameters

-

capacitor Capacitor matrix. rlayer Layer of the drawn vertical rectangle.

References RoutMatchedCapacitor.__stretchTopPlateCompactCap__(), CapacitorStack.matchingScheme, VerticalRoutingTracks.matchingScheme, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, CapacitorStack.nets, and VerticalRoutingTracks.nets.

Referenced by RoutMatchedCapacitor.route().

◆ __stretchTopPlateCompactCap__()

| def __stretchTopPlateCompactCap__ | ( | self, | |

| net, | |||

| capacitor, | |||

| routingLayer, | |||

j = 0 |

|||

| ) |

Draws vertical stretched layers for a given elementary capacitor.

References RoutMatchedCapacitor.__setStretchingDySourceDyTarget__(), and RoutMatchedCapacitor.topPlateStretching.

Referenced by RoutMatchedCapacitor.__stretchTopPlates__().

◆ __setStretchingDySourceDyTarget__()

| def __setStretchingDySourceDyTarget__ | ( | self, | |

| capacitor, | |||

| deltay | |||

| ) |

Sets the abcissas of the extremities of the vertical stretching to be applied to capacitor's top plates for a given elementary capacitor in the matrix.

- Parameters

-

capacitor .values() Elementary unit capacitor. deltay Stretching value.

- Returns

- A list that contains

dySourceanddyTargetas top extremity and bottom extermity, respectively.

Referenced by RoutMatchedCapacitor.__stretchTopPlateCompactCap__(), and RoutMatchedCapacitor.computeHRLayerYCenter().

◆ __computeConnections__()

| def __computeConnections__ | ( | self, | |

| i, | |||

| j, | |||

| capacitorIdentifier | |||

| ) |

Computes horizontal routing layers source and target abcissas for top and bottom plates connections to its associated routing track.

- Parameters

-

(i,j) row and column indexes, respectively, in the matrix which describe the elementary capacitor position in the matrix. capacitorIdentifier equal to '1' if C1 and '2' if C2.

- Returns

- A nested dicitionary. The overal dictionary is composed of keys equal to

topPlateand \d bottomPlate and values equal to sub-dictionaries. The sub-dictionaries, are in their turn composed of two keys standing for the abcissa of the source and the abcissa of the target.

- Remark:

- Naturally, an exception is raised if an unsupported capacitor identifier is given.

References RoutMatchedCapacitor.__findHRLDyTrarget__(), RoutMatchedCapacitor.__isCapacitorAdummy__(), RoutMatchedCapacitor.__setPlatesLabels__(), RoutMatchedCapacitor.capacitor, VerticalRoutingTracks.capacitor, VerticalRoutingTracks.capacitorIds, CapacitorStack.capacitorsNumber, VerticalRoutingTracks.capacitorsNumber, CapacitorStack.dummyElement, RoutMatchedCapacitor.dummyElement, VerticalRoutingTracks.dummyElement, CapacitorStack.dummyRing, RoutMatchedCapacitor.dummyRing, VerticalRoutingTracks.dummyRing, CapacitorUnit.getTopPlateRLayerXMin(), CapacitorStack.matchingScheme, VerticalRoutingTracks.matchingScheme, CapacitorStack.matrixDim, VerticalRoutingTracks.matrixDim, CapacitorStack.nets, VerticalRoutingTracks.nets, CapacitorStack.vRoutingTrack_width, VerticalRoutingTracks.vRoutingTrack_width, RoutMatchedCapacitor.vRoutingTrackXCenter, VerticalRoutingTracks.vRoutingTrackXCenter, RoutMatchedCapacitor.vRTInstance, RoutMatchedCapacitor.vRTsDistribution, and VerticalRoutingTracks.vRTsDistribution.

Referenced by RoutMatchedCapacitor.drawHRLayers().

The documentation for this class was generated from the following file:

- capacitorrouted.py